#### APPENDIX A

NOTE: This order is nonprecedential.

# UNITED STATES COURT OF APPEALS FOR THE FEDERAL CIRCUIT

POLARIS INNOVATIONS LIMITED.,  $Appellant, \\ v. \\ KINGSTON TECHNOLOGY COMPANY, INC., \\ Appellee$

## UNITED STATES, Intervenor

#### 2018-1768

Appeal from the United States Patent and Trademark Office, Patent Trial and Appeal Board in No. IPR2016-01621.

Decided: January 31, 2020

MATTHEW D. POWERS, Tensegrity Law Group LLP, Redwood Shores, CA argued for appellant. Also represented by Jennifer Robinson; Azra Hadzimehmedovic, Aaron Matthew Nathan, Samantha A. Jameson, McLean, VA; Nathan Nobu Lowenstein, Kenneth J. Weatherwax, Lowenstein & Weatherwax LLP, Los Angeles, CA.

MICHAEL JOHN BALLANCO, Fish & Richardson PC, Washington, DC, argued for appellee. Also represented by DAVID M. HOFFMAN, Austin, TX.

MELISSA N. PATTERSON, Appellate Staff, Civil Division, United States Department of Justice, Washington, DC, argued for intervenor. Also represented by Courtney Dixon, Dennis Fan, Scott R. McIntosh, Joseph H. Hunt; Thomas W. Krause, Joseph Matal, Farheena Yasmeen Rasheed, Office of the Solicitor, United States Patent and Trademark Office, Alexandria, VA.

Before REYNA. WALLACH, and HUGHES, *Circuit Judges*.

PER CURIAM.

In its opening brief, Polaris Innovations Limited argues that the final written decision at issue in this appeal exceeds the scope of the Patent Trial and Appeal Board's authority and violates the Constitution's Appointments Clause. See Appellant's Br. 52 (citing U.S. Const. art. II, § 2, cl. 2). This court recently decided this issue in Arthrex, Inc. v. Smith & Nephew, Inc., 941 F.3d 1320 (Fed. Cir. 2019). Accordingly, the Board's decision in No. IPR2016-01621 is vacated, and the case is remanded to the Board for proceedings consistent with this court's decision in Arthrex.

# VACATED AND REMANDED COSTS

No costs.

#### APPENDIX B

NOTE: This order is nonprecedential.

# UNITED STATES COURT OF APPEALS FOR THE FEDERAL CIRCUIT

POLARIS INNOVATIONS LIMITED.,  $Appellant, \\ v. \\ KINGSTON TECHNOLOGY COMPANY, INC., \\ Appellee$

# UNITED STATES, Intervenor

#### 2018-1831

Appeal from the United States Patent and Trademark Office, Patent Trial and Appeal Board in No. IPR2017-00116.

Decided: January 31, 2020

MATTHEW D. POWERS, Tensegrity Law Group LLP, Redwood Shores, CA argued for appellant. Also represented by Jennifer Robinson; Azra Hadzimehmedovic, Aaron Matthew Nathan, Samantha A. Jameson, McLean, VA; Nathan Nobu Lowenstein, Kenneth J. Weatherwax, Lowenstein & Weatherwax LLP, Los Angeles, CA.

DAVID M. HOFFMAN, Fish & Richardson PC, Austin, TX, argued for appellee. Also represented by

MICHAEL JOHN BALLANCO, Washington, DC; NIKITA GUPTA FIORELLA, Wilmington, DE

MELISSA N. PATTERSON, Appellate Staff, Civil Division, United States Department of Justice, Washington, DC, argued for intervenor. Also represented by Courtney Dixon, Dennis Fan, Scott R. McIntosh, Joseph H. Hunt; Thomas W. Krause, Joseph Matal, Farheena Yasmeen Rasheed, Office of the Solicitor, United States Patent and Trademark Office, Alexandria, VA.

Before REYNA. WALLACH, and HUGHES, Circuit Judges.

Opinion for the court filed PER CURIAM.

Concurring opinion filed by *Circuit Judge* HUGHES, in which *Circuit Judge* WALLACH joins.

PER CURIAM.

In its opening brief, Polaris Innovations Limited argues that the final written decision at issue in this appeal exceeds the scope of the Patent Trial and Board's authority Appeal and violates the Constitution's Appointments Clause. See Appellant's Br. 52 (citing U.S. Const. art. II, § 2, cl. 2). This court recently decided this issue in Arthrex, Inc. v. Smith & Nephew, Inc., 941 F.3d 1320 (Fed. Cir. 2019). Accordingly, the Board's decision in No. IPR2016-01621 is vacated, and the case is remanded to the Board for proceedings consistent with this court's decision in Arthrex.

# VACATED AND REMANDED COSTS

No costs.

NOTE: This order is nonprecedential.

# UNITED STATES COURT OF APPEALS FOR THE FEDERAL CIRCUIT

# POLARIS INNOVATIONS LIMITED., $Appellant, \\ \text{v.}$

# KINGSTON TECHNOLOGY COMPANY, INC., Appellee

### UNITED STATES, Intervenor

#### 2018-1831

Appeal from the United States Patent and Trademark Office, Patent Trial and Appeal Board in No. IPR2017-00116.

HUGHES, Circuit Judge, concurring, in which WALLACH, Circuit Judge, joins.

I concur because we are bound by the prior panel decision in *Arthrex*, *Inc.* v. *Smith & Nephew*, *Inc.*, 941 F.3d 1320 (Fed. Cir. 2019). However, I write

<sup>&</sup>lt;sup>1</sup> The parties have raised the same arguments on the merits of the Appointments Clause issue in both Polaris cases before this panel, Nos. 2018-1768 and 2018-1831. However, the government contends that Polaris waived its Appointments Clause challenge in No. 2018-1768 because it failed to make the argument before the Board in the first instance. I need not address the waiver issue because this concurrence addresses only the merits of the Appointments Clause argument. And I

separately to note that I disagree with the merits and question the remedy of the Arthrex panel decision. I believe that viewed in light of the Director's significant control over the activities of the Patent Trial and Appeal Board and Administrative Patent Judges, APJs are inferior officers already properly appointed by the Secretary of Commerce.

But if APJs are properly considered principal officers, I have grave doubts about the remedy Arthrex applied to fix their unconstitutional appointment. In the face of an unconstitutional statute, our role is to determine whether severance of the unconstitutional portion would be consistent with Congress's intent. Given the employment protections APJs and their predecessors have enjoyed for more than three decades, I find no legislative intent to divest APJs of their Title 5 removal cure alleged protections to any constitutional defect. Because the bar to find nonseverability is so high, though, I reluctantly agree with Arthrex's remedy.

Ι

None of the parties here or in *Arthrex* dispute that APJs are officers who exercise "significant authority pursuant to the laws of the United States." *Buckley v. Valeo*, 424 U.S. 1, 126 (1976) (per curiam). But "significant authority" marks the line between an officer and an employee, not a principal and an inferior officer. Despite being presented with the opportunity to do so, the Supreme Court has declined to "set forth an

address this concurrence to No. 2018-1831 because the parties agree the issue was pre-served there.

exclusive criterion for distinguishing between principal and inferior officers for Appointments Clause purposes." *Edmond v. United States*, 520 U.S. 651, 661 (1997).

Instead, the pertinent cases make clear that the hall-mark of an inferior officer is whether a presidentially-nominated and senate-confirmed principal officer "direct[s] and supervise[s] [her work] at some level." Id. at 663. Edmond does not lay out a more exacting test than this, and we should not endeavor to create one in its stead. The cases employ an extremely context-specific inquiry, which accounts for the unique systems of direction and supervision in each case. See infra Section I. Finally, Edmond also makes clear that the Appointments Clause seeks to "pre-serve political accountability relative to important government assignments." 520 U.S. at 663. The current structure for appointing, directing and supervising, and re-moving APJs allows such political accountability through the Director's significant, substantive supervision of APJs' work, and the ability to discipline and terminate APJs to promote the efficiency of the service.

Arthrex, in my view, pays insufficient attention to the significant ways in which the Director directs and super-vises the work of the APJs and, instead, focuses on whether the Director can single-handedly review and reverse Board decisions, and whether APJs are removable at will. In doing so, the Arthrex panel essentially distills the Supreme Court's direction and supervision test into two discrete questions: (1) are an officer's decisions reviewable by a principal officer and (2) is the officer removable at will? Be-cause I believe that the Supreme Court

would have announced such a simple test if it were proper, I respectfully disagree with the *Arthrex* panel decision that APJs are principal officers. The Director's power to direct and supervise the Board and individual APJs, along with the fact that APJs are already removable under the efficiency of the service standard, suffices to render APJs inferior officers.

#### Α

The Director may issue binding policy guidance, institute and reconsider institution of an *inter partes* review, select APJs to preside over an instituted *inter partes* review, single-handedly designate or dedesignate any final written decision as precedential, and convene a panel of three or more members of his choosing to consider rehearing any Board decision. The *Arthrex* panel categorized some of these as "powers of review" and others as "powers of supervision," but I view them all as significant tools of direction and supervision.

Arthrex recognized, "[t]he Director 'responsible for providing policy direction and management supervision' for the [United States Patent and Trademark Officel." 941 F.3d at 1331 (quoting 35 U.S.C.  $\S$  3(a)(2)(A)). Not only can the Director promulgate regulations governing inter partes review procedures, but he prospectively issue binding policy guidance "interpreting and applying the pa-tent trademark laws." Gov't. Br. 21. APJs must apply this guidance in all subsequent inter partes review proceedings. Such guidance might encompass, for instance, exemplary application of the law to specific fact patterns, such as those posed in pending cases. These powers provide the Director with control over the process and substance of Board decisions. Gov't. Br. 8, 21. And though the Director cannot directly reverse an individual Board decision that neglects to follow his guidance, APJs who do so risk discipline or removal under the efficiency of the service standard applicable under Title 5. See infra Section I C. Such binding guidance, and the consequences of failing to follow it, are powerful tools for control of an inferior officer.<sup>2</sup>

The Director also has unreviewable authority to institute *inter partes* review. 35 U.S.C. § 314(a), (d). *Cf. Free Enter. Fund v. Pub. Co. Accounting Oversight Bd.*, 561 U.S. 477, 504 (2010) (discussing the importance of the ability to "start, stop, or alter individual [PCAOB] investigations," even where the reviewing principal officer already had significant "power over [PCAOB] activities"). Though the Arthrex panel did not address the Director's ability to reconsider an institution decision, our precedent also holds that the Board 3 may reconsider and reverse its initial institution decision. *See, e.g., Medtronic, Inc. v. Robert Bosch Healthcare Sys., Inc.*, 839 F.3d 1382, 1385–86 (Fed. Cir. 2016) (explaining that "§ 318(a) contemplates that a proceeding can be

<sup>&</sup>lt;sup>2</sup> To be sure, I do not mean to suggest that the Director's extensive powers of supervision mean that he can dictate the outcome of a specific inter partes proceeding. Rather, his ability to issue guidance and designate precedential opinions provides the general type of supervision and control over APJs' decision-making that renders them inferior, not principal, officers.

<sup>&</sup>lt;sup>3</sup> The Director's delegation of his institution power to the Board does not diminish its existence. 37 C.F.R. § 42.4(a) (stating that "[t]he Board institutes the trial on behalf of the Director"). See also Ethicon Endo-Surgery, Inc. v. Covidien LP, 812 F.3d 1023, 1033 (Fed. Cir. 2016).

'dismissed' after it is instituted, and, as our prior cases have held, administrative agencies possess inherent authority to reconsider their decisions, subject to certain limitations, regardless of whether they possess explicit statutory authority to do so" (internal quotation and citation omitted)).

The Director also controls which APJs will hear any given instituted *inter partes* review. 35 U.S.C. § 6(c). In my view, this power of panel designation is a quintessential method of directing and controlling a subordinate. Importantly, I do not believe that in stating that the power to remove an officer at-will from federal employment is "a powerful tool for control of an inferior," Free Enterprise, 561 U.S. at 510 (internal quotation omitted), the Supreme Court meant that such removal power is the only effective form of control in the context of the Appointments Clause. For example, the Judge Advocate General in Edmond could remove the Court of Criminal Appeal judges from judicial service without cause, but not necessarily federal employment altogether. Edmond, 520 U.S. at 664. See also Free Enterprise, 561 U.S. at 510 (relying on both at-will removal authority and "the [SEC's] other oversight authority" in finding with "no hesitation" that the PCAOB members are inferior officers). That is akin to the Director's authority to designate which APJs will consider a certain case. And despite acknowledging that "when a statute is silent on removal, the power of removal presumptively incident to the power appointment[,]" the Arthrex panel declined to opine on the Director's ability to de-designate APJs from a panel under § 6(c). Arthrex, 941 F.3d at 1332. But Edmond referenced the ability to remove the judges

there "from [their] judicial assignment[s]," followed by a recognition of the potent power of removal. 520 U.S. at 664. If the Director's ability to control APJs plays a significant part in the unconstitutionality at issue, such that the remedy is to make APJs removable at will, the panel should have definitively addressed the Director's de-designation authority. Moreover, as outlined in Section I C, *infra*, APJs already may be disciplined or removed from federal employment under the routine efficiency of the service standard, which is not incompatible with discipline or removal for failing to follow the Director's binding guidance.

And the Director may continue to provide substantial direction and supervision after the Board issues its final written decision. As *Arthrex* discusses, the Director may convene a Precedential Opinion Panel (POP), of which the Director is a member, to consider whether to designate a decision as precedential. *Arthrex*, 941 F.3d at 1330. But I read the Standard Operating Procedures more broadly, such that the Director may also make a precedential designation or de-designation decision single-handedly,<sup>4</sup> thereby unilaterally establishing binding

<sup>&</sup>lt;sup>4</sup> "No decision will be designated or de-designated as precedential or informative without the approval of the Director. This SOP does not limit the authority of the Director to designate or de-designate decisions as precedential or informative, or to convene a Precedential Opinion Panel to review a matter, in his or her sole discretion without regard to the procedures set forth herein." Patent Trial and Ap-peal Board, Standard Operating Procedure 2 (Revision 10) at 1 (Standard Operating Procedure 2), available at https://www.uspto.gov/sites/default/files/documents/SOP 2%20R10%20FINAL.pdf.

on important authority constitutional questions and other exception-ally important issues. Standard Operating Procedure 2, at 3-4. Indeed, it appears that the Director has done so in at least sixteen cases in 2018 and 2019. See USPTO, Patent TrialAppealBoard *Precedential* and and informativedecisions, availableathttps://www.uspto.gov/patents-applica-tionprocess/patent-trial-and-appeal-board/precedentialinformative-decisions (listing decisions designated as precedential in the past year, where some are labeled as "Precedential Opinion Panel decision" and others are not). The Director may also convene a POP of his choice, of which he is by default a member, to consider whether to rehear and reverse any opinion. Standard Operating Procedure 2, at 4. And, the Director may "determine that a panel of more than three members is appropriate" and then choose those additional members as well. *Id.* Though the Arthrex panel recognized these powers, it dismissed them because the Di-rector has only one vote out of at least three. 941 F.3d at 1331–32. This assessment, however, fails to recognize the practical influence the Director wields with the power to hand-pick a panel, particularly when the Director sits on that panel. The Director's ability to unilaterally designate or de-designate a decision as precedential and to convene a POP of the size and composition of his choosing are there-fore important tools for the direction and supervision of the Board even after it issues a final written decision.<sup>5</sup>

<sup>&</sup>lt;sup>5</sup> The *Arthrex* panel's underestimation of the Director's power is particularly evident in light of this court's prior en banc decision in *In re Alappat*, 33 F.3d 1526 (Fed. Cir. 1994),

Combined, all of these powers illustrate that the Director has constitutionally significant means of direction and supervision over APJs—making them inferior officers un-der the rule of *Edmond*.

R

Despite the Director's significant powers of direction and supervision, the *Arthrex* panel concluded that APJs are principal officers in large part because no principal officer may "single-handedly review, nullify or reverse" the Board's decisions. *Arthrex*, 941 F.3d at 1329. But Supreme Court precedent does not require such power. And in the cases in which the Court emphasized a principal officer's power of review, that principal officer had less authority to direct and supervise an inferior

abrogated on other grounds by In re Bilski, 545 F.3d 943 (Fed. Cir. 2008). Alappat contained strong lan-guage about the ability to control the composition and size of panels. See, e.g., id. at 1535 (noting that "the Board is merely the highest level of the Examining Corps, and like all other members of the Examining Corps, the Board operates subject to the Commissioner's overall ultimate authority and responsibility"). While the duties of the Board and the Director have changed since Alappat was decided, the authority to determine the Board's composition for re-consideration of an examiner's patentability determination mirrors the current authority with respect to inter partes review. Compare 35 U.S.C. § 6(c) (2012) (giving the Director authority to designate "at least 3 members of the Patent Trial and Appeal Board" to review "[e]ach appeal, derivation proceeding, post-grant review, and inter partes review"), with 35 U.S.C. § 7(b) (1988) (giving the Commissioner power to designate "at least three members of the Board of Appeals and Interferences" to review "ad-verse decisions of examiners upon applications for pa-tents"). Therefore, I believe the panel should have at least discussed how Alappat's view of the power to control the Board might impact the Appointments Clause analysis.

officer's work ex ante than the Director has here.

In Edmond, for instance, the Court of Appeals for the Armed Forces, an Article I court, could review decisions of the Court of Criminal Appeals judges at issue. However, its scope of review was limited. Edmond, 520 U.S. at 665 (explaining that the Court of Appeals for the Armed Forces may only reevaluate the facts when there is no "competent evidence in the record to establish each element of the offense beyond a reasonable doubt"). And while the Judge General "exercise[d] Advocate administrative oversight" and could "prescribe uniform rules of procedure," he could "not attempt to influence (by threat of removal or other-wise) the outcome of individual proceedings." Id. at 664. Nonetheless, the Supreme Court found that the Court of Criminal Appeals judges were inferior, not principal, officers. In comparison, while the Director unilaterally decide to rehear or reverse a Board decision, he has many powers to direct and supervise APJs both ex ante and ex post, Section I A, supra, that no principal officer had in *Edmond*.

Similarly, in *Freytag v. Comm'r*, 501 U.S. 868 (1991), the Supreme Court considered the status of special trial judges appointed by the Tax Court, whose independent decision-making varied based on the type of case before them. The Court held that the special trial judges were inferior officers—not employees—when presiding over "declaratory judgment proceedings and limited-amount tax cases" be-cause they "render[ed] the decisions of the Tax Court" in those cases. *Id.* at 882. In doing so, the Court distinguished between cases in which the special trial judges acted as "inferior officers who

exercise independent authority," and cases in which they still had significant discretion but less independent authority. Id. The Court's analysis distinguished between inferior officer and employee; no-where did the Court suggest that special trial "in-dependent authority" decide iudges' declaratory judgment proceedings and limitedamount cases rendered them principal officers. See id. at 881–82. Most recently, the Court applied the framework ofFreytag in deciding administrative law judges (ALJs) of the Securities and Ex-change Commission (SEC) are inferior officers or employees. Lucia v. S.E.C., 138 S. Ct. 2044, 2053 (2018). The Court reasoned that SEC ALJs and *Freytag's* special trial judges are extremely similar, but SEC ALJs arguably wield more power because their decisions become final if the SEC declines review. Id. at 2053-54. But again, the Court found this structure still only rendered SEC ALJs officers, not employees. Id. at 2054. No mention was made of SEC ALJs being principal officers. 6 See id. at 2051 n.3 (explaining that the distinction between principal and inferior officers was "not at issue here"). Just as the special trial judges in Freytag and the SEC ALJs in *Lucia* were inferior officers, so too are APJs.

Nor does this court's precedent require unfettered review as a marker of inferior officer

<sup>&</sup>lt;sup>6</sup> In fact, the Court declined "to elaborate on *Buckley's* 'significant authority' test" marking the line between officer and employee, citing two parties' briefs which argued that the test between officer and employee, not principal and inferior officer, should include some measure of the finality of decision making. *Lucia*, 138 S. Ct. at 2051–52.

status. In Masias v. Sec'y of Health & Human Servs., we rebuffed the argument that because the Court of Federal Claims does not review decisions of the Vaccine Program's special masters de novo, the special masters are principal officers. 634 F.3d 1283, 1293–94 (Fed. Cir. 2011). There, we recognized that the Court of Federal Claims may only "set aside any findings of fact or conclusions of law of the special master found to be arbitrary, capricious, an abuse of discretion, or other-wise not in accordance with law . . . ." Id. at 1294. This limited review means that many of the special masters' decisions are effectively final because the Court of Federal Claims has no basis to set aside findings of fact or conclusions of law. We reasoned that such limited review of special masters' decisions by the Court of Federal Claims resembled the review in *Edmond*, and that "the fact that the review is limited does not mandate that special masters are necessarily 'principal officers." Id. at 1295.

Finally, the panel analogized the *Arthrex* issue to one addressed by the D.C. Circuit Intercollegiate Broad. Sys., Inc. v. Copyright Royalty Bd., 684 F.3d 1332 (D.C. Cir. 2012). See Arthrex, 941 F.3d at 1334. But the facts of *Intercollegiate* are significantly different than those in Arthrex, or here. The Librarian of Congress—the principal officer who supervises the Copyright Royalty Judges (CRJs) at issue—was much more constrained in her ability to direct and supervise the CRJs than the Director. The governing statute grants CRJs broad discretion over rate-making. See 17 U.S.C. § 802(f)(1)(A)(i) (stating that "[CRJs] shall have full independence in making" numerous copyright rate-related decisions). The

"ap-prov[es] the CRJs' Librarian procedural regulations, . . . issu[es] ethical rules for the CRJs, [and] . . . oversee[s] various logistical aspects of their duties," such as publishing CRJs' decisions and providing administrative resources. *Intercollegiate*, 684 F.3d at 1338. In fact, it appears the only way the Librarian can exercise substantive control over the CRJs' ratemaking decisions is indirectly through the Register of Copyrights, whom she, not the President, appoints. See 17 U.S.C. § 701(a). The Register corrects any legal errors in the CRJs' ratemaking decisions, 17 U.S.C. § 802(f)(1)(D), and provides written opinions to the CRJs on "novel question[s] of law," 17 U.S.C. § 802(f)(1)(B), or when the CRJ requests such an opinion. 17 U.S.C. § 802(f)(1)(A)(ii). But the CRJs may not consult with the Register about a question of fact. 17 U.S.C. § 802(f)(1)(A)(i). The Librarian therefore exerts far less control over CRJs than the Director can over APJs using all the powers of direction and supervision discussed in Section I A, supra.

The ill-suited comparison to *Intercollegiate* in *Arthrex* again highlights how the unique powers of direction and supervision in each case should be viewed in totality, rather than as discrete categories weighing in favor of inferior officer status or not. In particular, by breaking up the analysis into three discrete categories—Review, Supervision, and Removal—the *Arthrex* panel overlooks how the powers in each category impact each other. Again, for ex-ample, whereas ex post the Court of Appeals for the Armed Forces has more power to review the Court of Criminal Ap-peals judges' decisions than the Director has to review a Board decision, neither

the JAG nor the Court of Appeals for the Armed Forces have the Director's ex ante control, such as the power to decide whether to hear a case at all or to issue binding guidance on how to apply the law in a case. Viewed through this integrated lens, I believe APJs comfortably fit with prior Supreme Court precedent that has never found a principal officer in a challenged position to date.

C

Finally, to the extent that the Arthrex panel decision is based on the lack of review along with perceived impermissible restrictions on removal of APJs, I believe it misapprehends the applicable efficiency of the service standard that protects APJs. The efficiency of the service standard al-lows discipline and removal for "misconduct [that] is likely to have an adverse impact on the agency's performance of its functions." See Brown v. Dep't of the Navy, 229 F.3d 1356, 1358 (Fed. Cir. 2000). To be sure, the efficiency of the service standard does not allow discipline or removal of APJs "without cause," as in Edmond. See Arthrex, 941 F.3d at 1333. But neither the Supreme Court nor this court has required that a civil servant be removable at will to qualify as an inferior officer. To the contrary, the Supreme Court and this court have upheld for-cause removal limitations on inferior officers. See, e.g., Morrison v. Olson, 487 U.S. 654, 692–93 (1988) (holding that the "good cause" restriction on removal of the independent counsel, an inferior officer, is permissible); Masias, 634 F.3d at 1294 (stating that the Court of Federal Claims can remove special masters for "incompetency, misconduct, or neglect of duty or for physical or mental disability or for other

good cause shown"). See also Free Enterprise, 561 U.S. at 494 (explaining that the Court previously "adopted verbatim the reasoning of the Court of Claims, which had held that when Congress ' "vests the appointment of inferior officers in the heads of Departments[,] it may limit and restrict the power of removal as it deems best for the public interest' "(alteration in original) (quoting United States v. Perkins, 116 U.S. 483, 485 (1886) (itself quoting Perkins v. United States, 20 Ct. Cl. 438, 444 (1885)))).

The efficiency of the service standard allows supervisors to discipline and terminate employees for arguably even a wider range of reasons than the standards above, including failure or refusal to follow the Director's policy or legal guidance. Together with the significant authority the Director wields in directing and supervising APJs' work, the ability to remove an APJ on any grounds that promote the efficiency of the service supports finding that APJs are inferior officers.

#### П

Assuming for the sake of argument that APJs are principal officers, a remedy is required to cure the constitutional violation arising from their present appointment scheme. However, I do not believe that the remedy pro-posed by the *Arthrex* panel comports with congressional in-tent as evidenced by the employment protections provided to APJs and their predecessors for over thirty years. The *Arthrex* panel makes APJs removable at will by partially severing 35 U.S.C. § 3(c) as it applies Title 5's removal protections to APJs. *Arthrex*, 941 F.3d at 1337–38. I question whether Congress would have wanted to leave APJs with-out the removal

protections of Title 5. But, given the high standard for finding non-severability, I cannot say that the Arthrex panel's remedy was improper.

#### Α

Before proceeding to the traditional severance analysis, I must note several concerns about the purported "severance." In traditional severance cases, both the unconstitutional language being severed and the remaining language are usually part of one statute enacted at the same time. In what appears to be a smaller number of cases, an unconstitutional amendment was severed from the original statute. E.g., Reitz v. Mealey, 314 U.S. 33, 38-39 (1941), overruled in part on other grounds by Perez v. Campbell, 402 U.S. 637 (1971). But here the "severance" is far more convoluted—to the extent that I question whether "severance" is even the appropriate characterization of the *Arthrex* remedy.

A court may sever the application of a particular statute without striking language explicitly. See, e.g., Nat'l Fed'n of Indep. Bus. v. Sebelius, 567 U.S. 519, 586 (2012) (invalidating the application of a statute to cure a constitutional defect). But the Arthrex panel did not simply sever the application of 35 U.S.C. § 3(c) to APJs. It severed § 3(c)'s application of Title 5 protections, but only with respect to Title 5's removal protections, and only to APJs. See Arthrex, 941 F.3d at 1337–38. In doing so, it severed the application of a separate statute, indeed, a section in a separate title of the United States Code. Id. Further, the Title 5 employment protections afforded by 35 U.S.C. § 3(c) al-ready existed when Congress significantly amended other portions of Title 35, but made no changes to § 3(c), with the

America Invents Act in 2011. See infra Section II C. I question whether it is appropriate to solve the alleged constitutional infirmity at issue in Arthrex and in this case by severing the application of a statute that Congress left un-touched in its most recent revision, the substance of which had applied in various forms for over 30 years. See infra Section II B.

В

When faced with an unconstitutional statute, we must determine whether severing the offending portion is possible. To do so, we must determine if the remaining statute "will function in a manner consistent with the intent of Congress." *Alaska Airlines, Inc. v. Brock*, 480 U.S. 678, 685 (1987) (emphasis removed).

The question of severability is a weighty one and the bar for finding an unconstitutional provision non-severable is high. We "must refrain from invalidating more of the statute than is necessary. Indeed, we must retain those portions of the Act that are (1) constitutionally valid, (2) capable of 'functioning independently,' and (3) consistent with Congress' basic objectives in enacting the statute." *United States v. Booker*, 543 U.S. 220, 258–59, (2005) (internal citations omitted).

Because the statute as severed by *Arthrex* can function independently and is constitutionally valid, the key question is whether the statute as excised "remains consistent with Congress' initial and basic . . . intent." *Id.* at 264. Here, I question whether the *Arthrex*-excised statute does so. Congress afforded federal employment protections to

APJs and their predecessors for over thirty years. And it seems unlikely to me that Congress, faced with this Appointments Clause problem, would have chosen to strip APJs of their employment protections, rather than choose some other alternative. However, because the bar for non-severability is so high, and Congress can, at the end of the day, make another legislative choice if it disagrees with the outcome here, I reluctantly conclude that § 3(c) can be severed as it applies to the removal protections for APJs.

To be sure, I do not question the ability to sever an un-constitutional provision lightly. But our touchstone must remain the intent of Congress, and in this case, Congress has maintained federal employment protections for USPTO officers and employees, including APJs and their predecessors, from 1975 to today. This long-standing statutory protection leads me to believe that Congress intended for APJs to have removal protections, such as those incorporated through Title 5 in 35 U.S.C. § 3(c), regardless of changes made to the Board's duties in the AIA.

C

As the *Arthrex* panel noted, examiners-in-chief—"the former title of the current APJs"—were in fact nominated by the President and confirmed by the Senate until 1975. *Arthrex*, 941 F.3d at 1344. *See also* 35 U.S.C. § 3 (1952). But the 1975 amendment did not simply remove Presidential nomination and Senate confirmation; it instead pro-vided for the appointment of examiners-in-chief (1) by the Secretary of Commerce (2) "under the classified civil ser-vice." An Act To Amend Title 35, United States

Code, "Patents", and For Other Purposes, Pub. L. No. 93–601, secs. 1–2, §§ 3, 7, 88 Stat. 1956, 1956 (1975) (codified as amended at 35 U.S.C. §§ 3, 7 (1976)). This amendment provided federal employment protections to examiners-in-chief. See, e.g., Arnett v. Kennedy, 416 U.S. 134, 150–51 (1974), overruled in part on other grounds by Cleveland Bd. of Educ. v. Loudermill, 470 U.S. 532 (1985) (explaining that the Lloyd-LaFollette Act's "efficiency of the service" standard governed the dismissal of a competitive civil service employee); Cole v. Young, 351 U.S. 536, 543 (1956) (describing dismissal of federal employees as governed by "general personnel laws," such as the Lloyd-LaFollette Act's "efficiency of the service" standard).

Two reasons for this change appear in the legislative history. First, due to the growing number of examiners-in-chief, Presidential nomination and Senate confirmation posed a "burden." H.R. REP. NO. 93-856, at 2 (1974). In an early case discussing the Appointments Clause, the Supreme Court said that this was exactly the reason for providing for appointment of inferior officers by people other than the President. United States v. Germaine, 99 U.S. 509-10(1878).Second, the position examiner-in-chief "requir[es] unique legal technical qualifications and experience." An Act To Amend Title 35, United States Code, "Patents", and For Other Purposes: Hearing on S. 645, H.R. 5237, S. 1253 and S.1254 Before Subcomm. No. 3 of the H. Comm. on the Judiciary, 92d Cong. 28–29 (1974) (letter from William N. Letson, Acting General Counsel of the Dep't of Commerce, to Emanuel Celler, Chairman of the H. Comm. on the Judiciary).

change, In making this Congress implicitly recognized that APJs be-longed in the civil service, where expertise and nonpartisan decision-making are expected of all civil servants. Indeed, such ideas motivated the passage of the Civil Service Re-form Act (CSRA) only three years after Congress provided for the appointment of APJs through the civil service system. Lovshin v. Dep't of Navy, 767 F.2d 826, 832 (Fed. Cir. 1985) (citing the Senate's discussion of the public's right to a government that is both "efficient and effective" and "impartially administered").

Congress then maintained these federal employment protections through several amendments over more than three decades. In 1985, Congress amended 35 U.S.C. § 7, creating the Board of Patent Appeals and Interferences (BPAI) from the existing Board of Appeals, and again pro-vided that the examiners-in-chief "shall be appointed to the competitive service." Patent Law Amendment Acts of 1984, Pub. L. 98–622, title II, sec. 201, § 7(a), 98 Stat. 3383, 3386 (1984) (codified as amended at 35 U.S.C. § 7 (1988)). Though the 1978 CSRA replaced the Lloyd-LaFollette Act between the 1975 and 1985 amendments to 35 U.S.C. § 7, the CSRA maintained the "efficiency of the service" standard for discipline of dismissal federal employees competitive service. 5 U.S.C. § 7513 (1978). See also Cornelius v. Nutt, 472 U.S. 648, 669 (1985) ("The statutory phrase 'such cause as will promote the

<sup>&</sup>lt;sup>7</sup> For the Appointments Clause analysis here, I treat the terms "competitive service" and "classified civil service" as interchangeable. *See*, *e.g.*, 5 U.S.C. § 2102(c) (2018) ("As used in other Acts of Congress, 'classified civil service' or 'classified service' means the 'competitive service[.]").

efficiency of the ser-vice' pre-dates the Civil Service Reform Act's recognition of federal sector collective bargaining.") (Marshall, J., dissenting).

In 1999, Congress made four changes significant modified the statutory Congress language governing the BPAI, moving the Board's governing language from § 7 to its current location in § 6. See Patent and Trademark Office Efficiency Act, Pub. L. 106–113, ch. 1, sec. 4717, 113 Stat. 1501, 1501A-580 (1999) (codified at 35 U.S.C. § 6 (2000)). Second. introduced the terminology administrative patent judge, in place of examinersin-chief. Id. at 1501A-580-81. Third, Congress removed the previous language appointing examiners-in-chief under the competitive service, but added the current § 3(c), giving Title 5 protections to USPTO employees and officers. *Id.* at sec. 4713, § 3(c), 113 Stat. at 1501A-577 (codified as amended at 35 U.S.C. § 3(c) (2000)). This meant that even though their title changed, APJs remained subject to discipline or dismissal subject to the efficiency of the service standard. See 5 U.S.C. § 7513 (2000). Fourth, the amendment transferred the power to appoint APJs from the Secretary of Commerce to the Director. Patent and Trademark Office Efficiency Act, Pub. L. 106-113, ch. 1, sec. 4717, 113 Stat. 1501, 1501A-581 (1999) (codified at 35 U.S.C. § 6(a) (2000)).

This fourth change is particularly significant because only a few years later, Congress explicitly considered the constitutionality of this choice—whether APJs were employees that could be appointed by the Director or officers that must be appointed by the Secretary of Commerce. Congress

chose the latter. Consideration of this issue was prompted by an intellectual property law scholar's suggestion in 2007 that APJs were inferior officers, not employees, and therefore must be appointed by the President, a Court of Law, or the Head of a Department. See John F. Duffy, Are Administrative Patent Judges Unconstitutional?, 2007 PATENTLY-O PAT L.J. 21, 25 (2007). Congress responded swiftly, amending the law in 2008 to give the power to appoint APJs back to the Secretary of Commerce. Patent and Trademark Administrative Judges Appointment Authority Revision, Pub. L. 110–313, sec. 1, § 6, 122 Stat. 3014, 3014 (2008) (codified as amended at 35 U.S.C. § 6(a) (2012)). While some legislators viewed the fix as un-necessary, none suggested that APJs were in fact principal officers appointable only by the President. Compare 154 Cong. Rec. H7234 (daily ed. Jul. 29, 2008 edition) (statement of Rep. King) ("[A] straightforward reading of article II, section 2, which I strongly endorse, suggests the 1999 authority that Congress bestowed on the Patent and Trademark Office Director to appoint administrative law judges is unconstitutional, inconsistent with article II, section 2. Instead, this right is more properly reserved for . . . the Secretary of Commerce . . . . "), with id. (statement of Rep. Cohen) ("We firmly believe that made by the Director appointments are constitutional."). That Congress explicitly considered the constitutionality of APJ appointments just four years before passing the AIA, and confirmed their appointment by the Head of a Department, strongly suggests that Congress believed APJs were inferior officers in 2000, 2007, and 2011, and thus, could be constitutionally appointed by the Secretary, even

with restrictions on their removal.

Finally, though Congress made significant changes to Title 35 through the AIA, it did not modify § 3(c)'s application of Title 5 protections to USPTO employees and officers. § 35 U.S.C. § 3(c) (2012). Yet again, APJs remained subject to the efficiency of the service removal standard applicable to many federal employees.

Further confirmation regarding Congressional intent comes from the fact that § 3 provides specific, and limited, removal procedures for the Director and the Commissioner for Patents, as opposed to all other officers and employees subject to § 3(c). The Director may be removed only by the President. 35 U.S.C. § 3(a)(4). The Commissioner may be removed "for misconduct or nonsatisfactory performance" under her performance agreement, "without regard to the provisions of title 5." 35 U.S.C. § 3(b)(2)(C). That Congress described specific removal procedures for these two positions strongly implies it intended that all other USPTO employees and officers enjoy the Title 5 protections provided in § 3(c).

Given this unbroken line of federal employment protection afforded to APJs and their predecessors for over three decades, I question whether severing § 3(c)'s Title 5 removal protections for APJs "remains consistent with Congress' initial and basic . . . intent." *Booker*, 543 U.S. at 264. My concerns are not

<sup>&</sup>lt;sup>8</sup> The AIA did amend 35 U.S.C. § 3(b), see Leahy-Smith America Invents Act, Pub. L. 112-29, sec. 21, § 3(b), 125 Stat. 284, 336 (2011) (governing the Director's ability to fix pay for APJs), and 35 U.S.C. § 3(e)(2), id. at sec. 20 § 3(e)(2), 125 Stat. at 334 (technical amendment changing "this Act" to "that Act").

alleviated by the *Arthrex* panel's focus on Congress's intent as it pertained to the importance of *inter* partes review, without considering why Congress chose to provide Title 5 employment protections to APJs for decades. *See Arthrex*, 941 F.3d at 1337–38.

D

Finally, I am mindful of the Supreme Court's guidance that:

Our ability to devise a judicial remedy that does not entail quintessentially legislative work often de-pends on how clearly we have already articulated the background constitutional rules at issue and how easily we can articulate the remedy. . . . But distinctions making in murkv a constitutional con-text, where lineordrawing is inherently complex, may call for a 'far more serious invasion of the legislative domain' than we ought to undertake.

Ayotte v. Planned Parenthood of N. New England, 546 U.S. 320, 329–30 (2006) (quoting United States v. Nat'l Treasury Emps. Union, 513 U.S. 454, 479 n.26 (1995)). Given the limited extent of Appointments Clause jurisprudence and Congress's repeated decisions to provide federal employment protections to APJs for decades, I am particularly concerned that Arthrex's remedy constitutes an unwise invasion of the legislative domain.

I recognize that the *Arthrex* panel considered several potential fixes and chose the one it viewed both as constitutional and minimally disruptive. But removing long-standing employment protections from hundreds of APJs is quite disruptive. Given no

clear evidence that Congress would have intended such a drastic change, I would defer to Congress to fix the problem. This is a legislative problem best left to a legislative solution. Congress faces fewer constraints than we do in fixing an unconstitutional statute. For example, Congress might choose to: grant the Director unilateral review over all Board decisions; make the Chief PTAB Judge a presidential appointee and grant her review of all Board decisions; provide for review of Board decisions by a panel of three Presidential appointees at the USPTO (having created at least two such positions in addition to the Director); or provide for presidential appointment of all APJs.

In sum, I believe the Director currently exercises sufficient oversight and supervision of APJs to render them inferior officers under the Appointments Clause. But if APJs must be viewed as principal officers, I question curing the ensuing constitutional violation by removing their Title 5 removal protections because I believe it conflicts with Congress's intent.

#### 30a

#### APPENDIX C

NOTE: This order is nonprecedential.

# UNITED STATES COURT OF APPEALS FOR THE FEDERAL CIRCUIT

POLARIS INNOVATIONS LIMITED., Appellant,

v.

$\begin{array}{c} {\rm KINGSTON\ TECHNOLOGY\ COMPANY,\ INC.,} \\ {\it Appellee} \end{array}$

ANDREI IANCU, UNDER SECRETARY OF COMMERCE FOR INTELLECTUAL PROPERTY AND DIRECTOR OF THE UNITED STATES PATENT AND TRADEMARK OFFICE, Intervenor

#### 2019-1202

Appeal from the United States Patent and Trademark Office, Patent Trial and Appeal Board in No. IPR2016-01622.

#### **ORDER**

PER CURIAM.

In light of this court's decision in *Arthrex, Inc. v. Smith & Nephew, Inc.*, 941 F.3d 1320 (Fed. Cir. 2019), and the fact that Polaris Innovations Limited raised an Appointments Clause challenge in its opening brief in the above captioned case,

#### IT IS ORDERED THAT:

- (1) The oral argument scheduled for March 2, 2020 is cancelled and the case is removed from the calendar.

- (2) The Patent Trial and Appeal Board's decision in No. IPR2016-01622 is vacated and the case is remanded to the Board for proceedings consistent with the court's decision in *Arthrex*.

FOR THE COURT

January 27, 2020 Date /s/ Peter R. Marksteiner Peter R. Marksteiner Clerk of Court

#### 32a

#### APPENDIX D

Paper 8

Trials@uspto.gov Entered: February 15, 2017 571-272-7822

## UNITED STATES PATENT AND TRADEMARK **OFFICE**

# BEFORE THE PATENT TRIAL AND APPEAL BOARD

KINGSTON TECHNOLOGY COMPANY, INC., Petitioner, v.

POLARIS INNOVATIONS LTD., Patent Owner.

> Case IPR2016-01621 Patent 6,428,057 B1

Before SALLY C. MEDLEY, JEAN R. HOMERE, and KEN B. BARRETT, Administrative Patent Judges.

HOMERE, Administrative Patent Judge.

**DECISION** Granting Institution of Inter Partes Review 37 C.F.R. § 42.108

#### I. INTRODUCTION

Kingston Technology Company, Inc. ("Petitioner") filed a Petition for *inter partes* review of claims 1–17 of U.S. Patent No. 6,438,057 B1 (Ex. 1001, "the '057 patent"). Paper 3 ("Pet."). Polaris Innovations Ltd. ("Patent Owner") filed a Preliminary Response. Paper 8 ("Prelim. Resp."). Institution of an *inter partes* review is authorized by statute when "the information presented in the petition . . . and any response . . . shows that there is a reasonable likelihood that the petitioner would prevail with respect to at least 1 of the claims challenged in the petition." 35 U.S.C. § 314(a); see 37 C.F.R. § 42.108.

Upon consideration of the Petition and Preliminary Response, we conclude the information presented shows there is a reasonable likelihood that Petitioner would prevail in establishing the unpatentability of claims 1–17 of the '057 patent.

#### A. Related Matters

The parties state that the '057 patent is the subject of a pending lawsuit in the Central District of California Southern Division that includes assertions against Petitioner. Pet. 2; Paper 5 (Patent Owner's Mandatory Notice), 1; Ex. 1002.

#### B. The '057 Patent

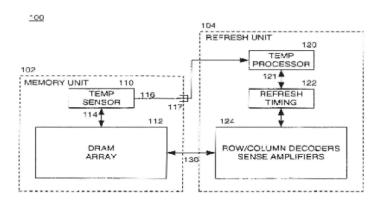

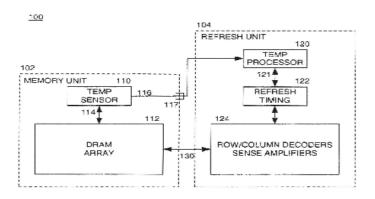

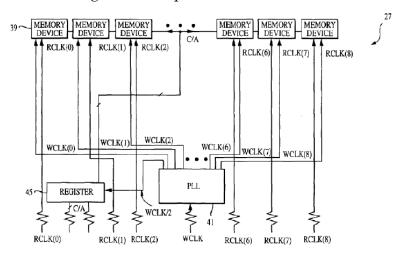

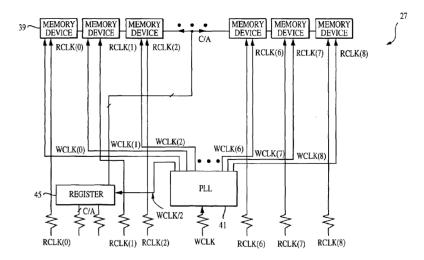

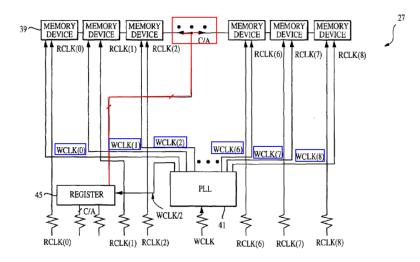

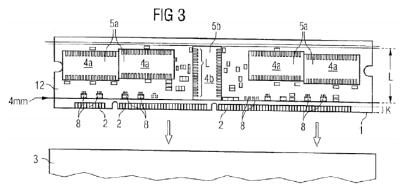

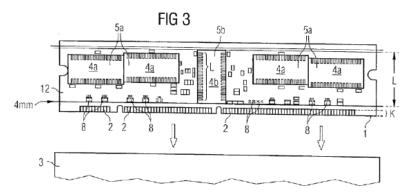

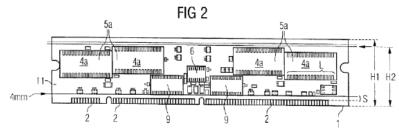

The '057 patent is directed to a method and system for refreshing the contents of a dynamic random access memory (DRAM) array. Ex. 1001, 1:5–7. In particular, the temperature of the DRAM array is utilized to adjust a refresh rate at which the contents of the DRAM array are updated. *Id.* at 1:7–10. Figure 3 of the '057 patent is reproduced below:

FIG. 3

Figure 3 illustrates system 100 for storing data in DRAM array 112. Id. at 4:11–12. In particular, Figure 3 depicts memory unit 102 containing temperature sensor 110 coupled to DRAM array 112, wherein memory unit 102 is connected to refresh unit 104 containing temperature processor 120 coupled to refresh timing 122 and row/column decoders sense amplifiers 124. Id. at 4:12–30. According to the '057 patent, "the DRAM array 112 may be implemented on a semiconductor chip and the temperature sensor 110 may be thermally coupled to the same semiconductor chip or to an intermediate member that thermal communication with the semiconductor chip." Id. at 4:22-26.

More specifically, in system 100 illustrated in Figure 3, upon receiving signal 116 from temperature sensor 110 indicating a temperature sensed from DRAM array 112, refresh unit 104 produces refresh signal 130 to refresh DRAM array 112 at a rate that varies in response to received

temperature signal 116. Id. at 4:30-32. Preferably, DRAM array 112 is refreshed at a rate that decreases as the temperature of DRAM array 112 decreases. Conversely, DRAM array 112 is refreshed at a rate that increases as the temperature of DRAM array 112 increases. Id. at 4:33-37. Further, according to the '057 patent, "the temperature sensor 110 and the DRAM array 112 are preferably disposed in a semiconductor package where the package includes at least one connection pin 117 operable to provide the signal on line 116 to external circuitry, such as the refresh unit 104." Id. at 4:49-"[T]he temperature sensor 110 preferably includes at least one diode 140 having a forward voltage drop that varies as a function of the temperature of the DRAM array 112." Ex. 1001 at 5:17-20.

#### C. Illustrative Claim

Petitioner challenges claims 1–17 of the '057 patent. Pet. 9. Claims 1, 13, and 16 are independent claims. Claims 2–12 depend either directly or indirectly from claim 1. Claims 14 and 15 depend either directly or indirectly from claim 13. Claim 17 depends from claim 16. *Id.* at 5:60–8:13.

Independent claim 1, reproduced below, is illustrative of the claimed subject matter:

## 1. An apparatus, comprising:

a semiconductor package including at least one connection pin;

at least one dynamic random access memory (DRAM) array disposed within the package; and at least one temperature sensor in thermal communication with the DRAM array, operable to produce a signal indicative of a temperature of the DRAM array, and coupled to the at least one connection pin such that the signal may be provided to external circuitry,

wherein the DRAM array is refreshed at a rate that decreases as the temperature of the DRAM array decreases and that increases as the temperature of the DRAM array increases.

#### Id. at 5:60–6:7.

Independent claim 13 is similar to claim 1, except that it includes a DRAM chipset comprising a "DRAM chip including a DRAM array and at least a temperature sensor" and one "refresh chip operable to refresh the DRAM array." *Id.* at 6:59–7:6. Independent claim 16 is similar to claim 1, except that it sets forth a method for refreshing contents of a DRAM array at a rate that varies proportionally in response to temperature increases/decreases of the DRAM array. *Id.* at 8:1–9.

#### D. Asserted Grounds of Unpatentability

Petitioner asserts that claims 1–17 are unpatentable based on the following grounds (Pet. 9–10):

| Reference(s)          | Basis    | Challenged Claims  |

|-----------------------|----------|--------------------|

| Atkinson <sup>1</sup> | § 103(a) | 1-17               |

| Atkinson and          | § 103(a) | 1, 3, 5-9, 12, 13, |

<sup>&</sup>lt;sup>1</sup> US 6,134,167, issued Oct. 17, 2000 (Ex. 1010) ("Atkinson").

| Broadwater et al. <sup>2</sup>  |          | and 16                |

|---------------------------------|----------|-----------------------|

| Atkinson,                       | § 103(a) | 2, 4, 10, 11, 14, 15, |

| Broadwater, and                 |          | and 17                |

| Miller et al. <sup>34</sup>     |          |                       |

| Tillinghast et al. <sup>5</sup> | § 103(a) | 1-17                  |

| and Broadwater                  |          |                       |

| Kodama <sup>6</sup> and Lee et  | § 103(a) | 1-17                  |

| al. <sup>7</sup> or Broadwater  |          |                       |

#### II. DISCUSSION

#### A. Claim Construction

In an *inter partes* review, we construe claim terms in an unexpired patent according to their broadest reasonable construction in light of the specification of the patent in which they appear. 37 C.F.R. § 42.100(b).

Consistent with the broadest reasonable construction, claim terms are presumed to have their ordinary and customary meaning as understood by a person of ordinary skill in the art in the context of the entire patent disclosure. *In re Translogic Tech.*, *Inc.*, 504 F.3d 1249, 1257 (Fed. Cir. 2007).

Patent Owner contends that because Petitioner

$<sup>^{2}</sup>$  US 4,970,497, issued Nov. 13, 1990 (Ex. 1006) ("Broadwater").

<sup>&</sup>lt;sup>3</sup> US 3,812,717, issued May 28, 1974 (Ex. 1015) ("Miller").

<sup>&</sup>lt;sup>4</sup> Although Miller is omitted from Petitioner's summary of asserted grounds, it is nevertheless relied upon in Petitioner's analysis of claims 2, 4, 10, 11, 14, 15, and 17. See, e.g., Pet. 20. We, therefore, treat Petitioner's analysis of claims 2, 4, 10, 11, 14, 15, and 17 based upon Atkinson, Broadwater, and Miller from the statement as a separate ground of unpatentability.

<sup>&</sup>lt;sup>5</sup> US 5,278,796, issued Jan. 11, 1994 (Ex. 1009) ("Tillinghast").

<sup>&</sup>lt;sup>6</sup> US 3,851,316, issued Nov. 26, 1974 (Ex. 1004) ("Kodama").

<sup>&</sup>lt;sup>7</sup> US 5,229,970, issued July 20, 1993 (Ex. 1011) ("Lee").

has not provided in the Petition how each of the challenged claims is to be construed, but instead advises the Board that the claims are to be construed according to their broadest reasonable interpretation. Petitioner has failed to demonstrate a scope of the claimed invention that permits the Board to apply the asserted references to the claims. Prelim. Resp. 5, 8. Further, Patent Owner contends that because Petitioner previously argued in the companion district court litigation that eight different claim terms are indefinite and cannot be construed, Petitioner cannot now request the Board to construe those claim terms according to their broadest reasonable interpretation ("BRI"). *Id.* at 5– 7. Patent Owner therefore submits that Petitioner has failed to meet its burden to demonstrate, with reasonable certainty, the scope of the claims to which the Board is to apply the alleged prior art. *Id*. at 7–9.

As set forth above and as correctly noted by the parties, we construe claim terms in an unexpired according to the broadest reasonable interpretation. Pet. 11 (citing Cuozzo Speed Techs. LLC v. Lee, 136 S. Ct. 2131, 2142–46 (2016); Prelim. Resp. 8. Neither party argues that a claim term is indefinite, and we are not persuaded by Patent Owner's reference to Petitioner's prior allegation of indefiniteness of certain claim terms in the district court proceeding that any of those terms are indefinite. Further, neither party proffers construction of, or otherwise disputes the meaning of, any of the claim terms. We determine, at this juncture of the proceeding, that it is not necessary to provide any express interpretation of the claim

terms. Only terms that are in controversy need to be construed, and then only to the extent necessary to resolve the controversy. *Vivid Techs., Inc. v. Am. Sci. & Eng'g, Inc.*, 200 F.3d 795, 803 (Fed. Cir. 1999).

# B. Asserted Obviousness over Atkinson and Broadwater

Petitioner contends claims 1, 3, 5–9, 12, 13, and 16 are unpatentable under 35 U.S.C. § 103(a) over the combination of Atkinson and Broadwater. Pet. 29–32 (referencing *id.* at 12–28). Relying on the declaration of Dr. Vivek Subramanian, Petitioner explains how the proposed combination of references discloses all of the claim limitations. *Id.* at 12–19, 23–32 (citing Ex. 1005).

#### 1. Atkinson

Atkinson describes a technique for reducing the consumption of electric power in the main computer memory. Ex. 1010, 1:16–20. In particular, Atkinson discloses a refresh logic device that generates a memory refresh signal having a rate, which varies proportionally with the sensed temperature of the computer memory. *Id.* at 5:61–66, 7:41–44.

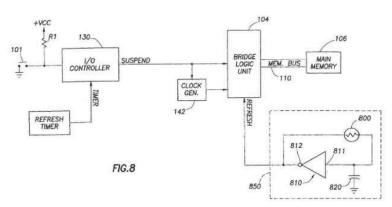

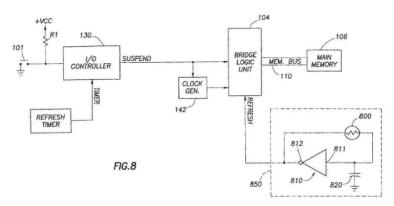

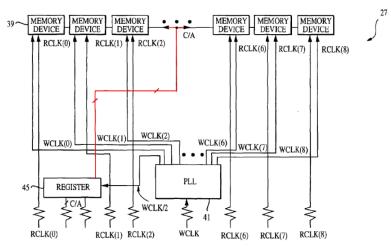

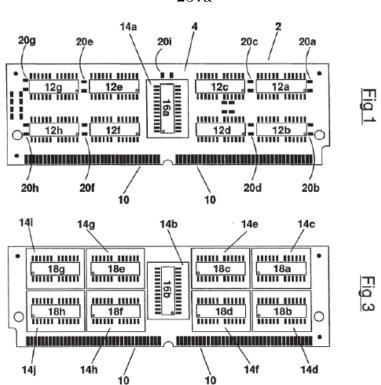

Figure 8 of Atkinson is reproduced below.

As illustrated in Figure 8 of Atkinson, refresh generator 850 includes thermistor 800, temperature of which drops upon sensing decreased temperature of main memory 106 to thereby produce a decrease of the rate of the refresh signal. Id. at 22:39-65. "Accordingly, the refresh temperature of the thermistor 800 represents the temperature of the memory storage logic 930, and the refresh frequency decreases approximately in proportion to the decrease in the temperature of the memory storage logic 930." Id. at 24:11-17. Conversely, when the temperature of thermistor 800 increases upon sensing an increased temperature of main memory 106, refresh generator 850 increases the rate of the refresh signal. Id. at 7:41-44, 21:38-Atkinson also discloses an alternative embodiment in which refresh generator including thermistor 800, is integrated in main memory 906. Id. at 23:37-40, 24:11-13, 24:22-23, Fig. 9.

Atkinson further discloses that that main memory 906 is an alternative embodiment of main memory 106 that preferably comprises DRAM

circuitry (*id.* at 23:32–34), but may also be other types of DRAM, such as synchronous DRAM (SDRAM), extended data output DRAM (EDO RAM), and Rambus RAM. *Id.* at 3:38–46, 9:1–5. Main memory 106 is connected to bus 110 to exchange signals therewith. *Id.* at 12:4–7.

#### 2. Broadwater

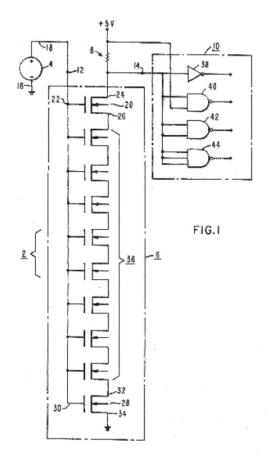

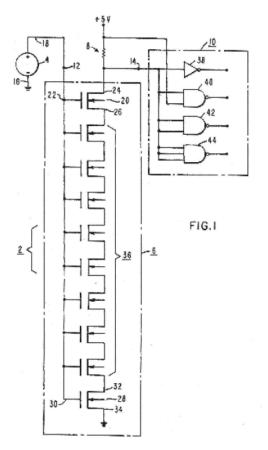

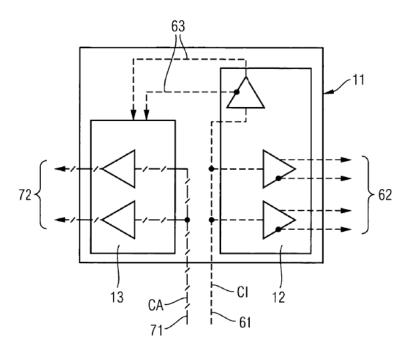

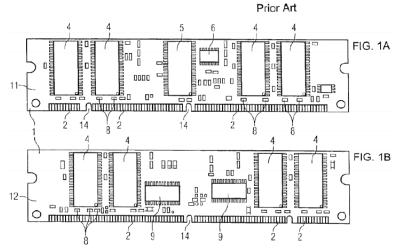

Broadwater relates to a technique for sensing and reducing the effects of thermal stress on packaged semiconductor chips. Ex. 1006, 1:6–8, Abstract. Figure 1 of Broadwater is reproduced below:

As depicted in Figure 1 above, Broadwater describes a chip package having thermal stress sensing circuit 6 with input 12 and output 14. *Id.* at 4:3:31–35. The voltage at output 14 varies as a function of input voltage and temperature. *Id.* at 4:39–41, Fig. 2. Output 14 can be routed to gate array 10, as shown, or can be provided to an external pin of the chip package. *Id.* at 4:31–53.

## 3. Discussion

Petitioner asserts that the combination of

Atkinson and Broadwater discloses the elements of claims 1, 3, 5–9, 12, 13, and 16. Pet. 12–32. We begin our analysis with claim 1. The preamble of claim 1 recites "an apparatus comprising." Ex. 1001, 5:61. Petitioner contends that Atkinson's description of an apparatus containing a main memory with a temperature sensor discloses the preamble of claim 1. Pet. 12.

Claim 1 next recites "a semiconductor package including at least one connection pin." Ex. 1001, Petitioner contends that 5:62–63. Atkinson's description of main memory 106 including any suitable type of memory such as DRAM or any of the special types of DRAM devices (e.g., SDRAM, EDO DRAM. Rambus DRAM) discloses "semiconductor package" because "one of ordinary skill in the art would know that SDRAM and Rambus DRAM are packaged semiconductor chips." Pet. 13 (citing Ex. 1005 ¶ 41; Ex. 1007, 524; Ex. 1010, 4:31–35, 8:65–9:5). Further, Petitioner asserts that Atkinson's description of main memory connection to bus 110 discloses the "connection pin" because one of ordinary skill would appreciate that "as the main memory is composed of packaged memory chips that receive a variety of bus signals," its "connections to the memory bus 110 would necessarily require at least one connection pin or it would be obvious to have one." Id. at 13–14 (citing Ex. 1010, 12:4–7, 23:32–37, 12:8–12; Ex. 1005 ¶ 42).

Claim 1 also recites "at least one dynamic random access memory (DRAM) array disposed within the package." Ex. 1001, 5:64–65. Petitioner asserts that Atkinson's description of a "computer system where the main memory 106 includes an

array of memory devices such as DRAM" discloses the "package" having disposed therein the DRAM array. Pet. 14 (citing Ex. 1010, Figs. 1, 4A, 5, 7–9, 5:57–62, 8:37–9:15; Ex. 1005 ¶ 43).

Claim 1 further recites "at least one temperature sensor in thermal communication with the DRAM array, operable to produce a signal indicative of a temperature of the DRAM array." Ex. 1001, 5:66-6:1. Petitioner asserts Atkinson's description of refresh generator 850, including thermistor 800 that directly senses the temperature of the DRAM, discloses "the temperature sensor . . . in thermal communication with the DRAM array." Pet. 14–16 (citing Ex. 1010, 22:52-62, 22:39-67, 23:32-37, 24:1-26, Fig. 8; Ex. 1005 ¶¶ 44, 45). Further, Petitioner asserts Atkinson describes an alternate embodiment wherein a "voltage controlled oscillator [(VCO)] combined with the temperature sensor could replace the refresh generator," such that "the temperature sensor couples to main memory 106, providing a voltage to the VCO that represents the main memory temperature." Pet. 16 (citing Ex. 1010, 23:5–19). The refresh signal produced by the VCO varies with the temperature of the memory device as sensed by the temperature sensor. Pet. 16–17 (citing Ex. 1010, 6:46-62, 7:46-48).

Claim 1 also recites "coupled to the at least one connection pin such that the signal may be provided to external circuitry." Ex. 1001, 6:2–3. Petitioner asserts that Atkinson describes an on-chip embodiment wherein a temperature sensor coupled directly to main memory 106 provides a voltage to the VCO that represents the main memory temperature. Pet. 17 (citing Ex. 1010, 23:15–17, Fig.

8; Ex. 1005 ¶ 47). According to Petitioner, while the on-chip embodiment described by Atkinson does not disclose providing the temperature signal to an external circuit, such a modification would have been obvious to one of ordinary skill in the art, particularly in view of Broadwater's disclosure of an external pin of a chip package (e.g., DRAM memory chip) for outputting a signal indicative of the chip's temperature. Id. (citing Ex. 1005 ¶¶ 47–49); id. at 30 (citing Ex. 1006, 4:31–33, 4:49–53; Ex. 1005 ¶¶ 83– 84). Further, Petitioner asserts that the ordinarily skilled artisan would have been motivated to combine the cited disclosures of Atkinson and Broadwater because Broadwater's disclosure adding an external pin to an existing chip package (e.g., Atkinson's DRAM) would help reduce the effects of thermal stress on the DRAM. Id. at 31 1006, 1:14–29; Ex. (citing Ex. 1005 Additionally, Petitioner concludes that the ordinarily skilled artisan would have recognized that the proposed combination would help maximize power saving during the self-refresh timing sequence. *Id*. (citing Ex  $1005 \, \P \, 86$ ).

Claim 1 also recites "wherein the DRAM array is refreshed at a rate that decreases as the temperature of the DRAM array decreases and that increases as the temperature of the DRAM array increases." Ex. 1001, 4:4–7. Petitioner asserts Atkinson describes a refresh logic that reduces the rate of the refresh signal in response to receiving a signal from the temperature sensor indicating a drop in the main memory temperature. Pet. 19 (citing Ex. 1010, 13:13–15, 22:2–7). Conversely, the refresh logic increases the rate of the refresh signal in response to

receiving a signal indicating an increase in the temperature of the main memory. Id. (citing 1010, 7:41–44; Ex. 1005 ¶¶ 50–51). According to Petitioner, the refresh frequency increases or decreases in proportion to the increase or decrease in the temperature of the DRAM as a way to achieve the greatest power savings. Id. (citing Ex. 1010, 20:53–56, 24:3–17, Fig. 6; Ex. 1005 ¶ 51).

Independent claims 13 and 16 are similar to claim 1. Petitioner has made a showing with respect to claims 13 and 16 similar to its showing with respect to claim 1. See, e.g., Pet. 26–28. To the extent that claims 13 and 16 are different from claim 1, Petitioner has accounted for such differences. We also have reviewed Petitioner's showing with respect to dependent claims 3, 5–9, and 12. Id. at 21, 23–26.

Patent Owner argues that Petitioner has not accounted sufficiently for each limitation and has not articulated sufficiently a reason to combine the prior art references. Prelim. Resp. 12–34. We address each argument in turn.

Patent Owner contends that Petitioner does not identify in Atkinson a semiconductor package including a "connection pin," as required by independent claims 1 and 13. *Id.* at 13. This argument is not persuasive. As discussed above, Petitioner reasoned that "[a]s the main memory is composed of packaged memory chips that receive a variety of memory bus signals, one of ordinary skill in the art would appreciate that connections to the memory bus 110 would necessarily require at least one connection pin, or it would be obvious to have one." Pet. 13–14 (citing Ex 1005 ¶¶ 41, 42). Further,

at this stage of the proceeding, Dr. Subramanian's testimony is unrebutted. For the foregoing reasons, we agree, on this record, with Petitioner's reasoning.

Patent Owner contends similarly that Petitioner does not demonstrate that the Atkinson-Broadwater combination includes a connection pin that provides a signal to external circuitry. Prelim. Resp. 31–32. As just discussed, however, we are persuaded, on this record, by Petitioner's argument that the limitation of providing the temperature signal to an external circuit is taught by the proposed combination of Atkinson's on-chip embodiment with Broadwater's an external pin of a chip package (e.g., DRAM memory chip) for outputting a signal indicative of the chip's temperature. Pet. 30.

Further, Patent Owner argues that Petitioner does not provide a motivation to combine Atkinson with Broadwater. Id. at 32–34. This argument is unavailing. Petitioner asserts the ordinarily skilled artisan would be motivated to combine the cited disclosures of Atkinson and Broadwater because Broadwater's disclosure of adding an external pin to Atkinson's DRAM would help reduce the effects of thermal stress on the DRAM, and would help maximize power saving during the self-refresh timing sequence. Id. at 31 (citing Ex. 1005 ¶¶ 85, 86). Dr. Subramanian's At this stage, moreover, testimony is unrebutted. We are persuaded, on this record, that Petitioner has provided an articulated reasoning with some rational underpinning sufficient to support the legal conclusion of obviousness. KSR Int'l Co. v. Teleflex Inc., 550 U.S. 398, 418 (2007) (citing In re Kahn, 441 F.3d 977, 988) (Fed. Cir. 2006)).

Patent Owner also argues that "Petitioner does not provide evidence dictating that the rate 'varies in response to the *signal*, as [claim 6] requires." Prelim. Resp. 23–26. In particular, Patent Owner argues that the cited portion of Atkinson "may well demonstrate that the rate and the temperature are linked," but does not teach "that it is the signal that causes the rate to decrease in proportion to the decrease in temperature." *Id.* at 23 (emphasis added). This argument is not persuasive. The antecedent basis for "the signal" is in claim 1, where Petitioner relies upon Atkinson's teaching of the refresh generator output, which is indicative of temperature of the DRAM asmeasured thermistor 800. Pet. 14-17 (discussing embodiments described in Figures 8 and 9 of Atkinson). In connection with the embodiment of Figure 8. Atkinson teaches explicitly that "[t]he frequency of the refresh signal in this embodiment continuously reduces as temperature decreases, rather than in discrete steps as in prior embodiments. Thus, refresh generator 850 provides a refresh signal that closely follows the temperature/frequency response of curve 600 or any other desired temperature/frequency response curve." Ex. 1010, 22:62-23:1. As a result, we agree with and are persuaded by Petitioner's contentions that Atkinson teaches refreshing the DRAM array at a rate that varies in response to the signal, as claim 6 requires, and not merely in response to the temperature of the DRAM array, as Patent Owner suggests.

Patent Owner also argues that Petitioner's contentions with respect to claim 7 are inconsistent with positions taken by Petitioner in the

corresponding district court litigation. Prelim. Resp. 26–27. This argument is not persuasive. As noted above, neither party argues in this proceeding that the term "refresh unit" recited in claim 7 is a meansterm or plus-function that itis indefinite. Consequently, Patent Owner's reference Petitioner's prior construction of "refresh unit" in the district court proceeding is not persuasive. On this record, we are persuaded that Atkinson's voltage controller oscillator (VCO) describes the refresh timing unit. Pet. 23-24.

Patent Owner also argues that Petitioner's contentions with respect to claims 8 and 9 rely on two distinct embodiments of Atkinson without explaining "how or why one would combine the two embodiments." Prelim. Resp. 28. This argument is not persuasive. Although Atkinson describes a first embodiment including refresh generator 850, and another embodiment wherein the refresh generator is replaced with the VCO combined with a temperature sensor, Petitioner does not rely upon embodiments the two cited to describe limitations claims 8 and 9. Instead, Petitioner relies only upon the latter embodiment to meet the claim limitations. See Pet. 24–25. Even if Petitioner relied upon both embodiments to support the assertion of obviousness, such a combination necessarily be improper because this ground is based upon obviousness rather than anticipation.

Finally, with respect to claim 13, Patent Owner argues that Petitioner has not identified with sufficient clarity what in Atkinson teaches the recited "DRAM chip," "refresh chip," "connection pin," or "external circuitry." Prelim. Resp. 29–30. We

disagree. As noted above, Petitioner has made a showing with respect to claim 13 similar to its showing with respect to claim 1. See, e.g., Pet. 26–28. To the extent that claim 13 is different from claim 1, Petitioner has accounted for such differences. Id.

Based on the current record before us, we determine that there is a reasonable likelihood that Petitioner would prevail in establishing that claims 1, 3, 5–9, 12, 13, and 16 are unpatentable over the combination of Atkinson and Broadwater.

# C. Asserted Obviousness over Atkinson, Broadwater, and Miller

Petitioner contends claims 2, 4, 10, 11, 14, 15, and 17 are unpatentable under 35 U.S.C. § 103(a) as obvious over the combination of Atkinson, Broadwater, and Miller.<sup>8</sup> Pet. 20–21, 22, 25, 27, 28, and 29–30. Relying on the declaration of Dr. Subramanian, Petitioner explains how the proposed combination of references discloses all of the claim limitations. *Id.* (citing Ex. 1005).

On this record, Petitioner has accounted sufficiently for the limitations of claims 2, 4, 10, 11, 14, 15, and 17. For example, claim 2 depends directly from claim 1 and recites "wherein the at least one temperature sensor includes at least one diode having a forward voltage drop that varies as a function of the temperature of the DRAM array, and the signal corresponds to the forward voltage drop of the at least one diode." Ex. 1001, 6:8–12.

Petitioner asserts that, although the '057 patent includes a diode as a known temperature sensor, it

<sup>&</sup>lt;sup>8</sup> See supra note 4.

also discloses other known temperature sensors (e.g., thermocouples, thermistors, or any other device that provides an output signal varying as a function of temperature). Pet. 20 (citing Ex. 1001, 2:42-45). Petitioner further asserts that Atkinson similarly discloses the use of such known temperature sensors thermocouple temperature or sensing integrated circuit). Id. (citing Ex. 1010, 22:21–24; Ex.  $1005 \P \P 52, 53$ ). Petitioner then contends that, at the time of the invention, measuring a forward voltage drop across a semiconductor diode to thereby read the temperature, as described in Miller, was a wellknown use of such a type of temperature sensor. Pet. 20 (citing Ex. 1015, Abstract). Petitioner concludes it would have been obvious to one of ordinary skill in the art to select a diode as a well-known type of temperature sensor for reading the temperature of Atkinson's DRAM. Id. at 21 (citing Ex. 1010, 24:63-65; 1005¶ 53).

Likewise, claim 4 depends directly from claim 1, and recites

wherein the at least one temperature sensor includes having a forward voltage drop that varies as a function of the temperature of the DRAM array; the at least one connection pin includes a first pin coupled to an anode of the diode and a second pin coupled to the cathode of the diode; and the signal corresponds to a potential voltage between the first and second pins.

Ex. 1001, 6:17–23.

Petitioner explains, with supporting evidence, that at the time of the invention, "given that the claim merely recites 'first pin' and 'second pin,' the diode temperature sensor would necessarily be connected to a first pin and a second pin if it were operational." Id. at 22 (citing Ex. 1005 ¶ 56). Petitioner further explains that "in such a diode configuration, the signal between the first pin and the second pin would necessarily be the forward voltage drop of the diode, which claim 4 defines as the signal." Id. Petitioner concludes that it would have been obvious to one of ordinary skill in the art at the time of the invention to "modify Atkinson to use a diode configuration as recited in claim 4 (which is essentially the same as the obvious variant in claim 2)." Id.

We also have reviewed the Petition with respect to dependent claims 10, 11, 14, 15, and 17, and determine that at this juncture of the proceeding Petitioner has accounted sufficiently for the recited limitations. Pet. 25, 27 and 28.

Patent Owner argues that Petitioner's reliance on "finite alternate types of integrated circuits for detecting temperatures" is a misapplication of KSR because the number of available alternatives is "far from 'small or easily traversed." Prelim. Resp. 19–23(citing Ortho-McNeill Pharmaceutical, Inc., v. Mylan Laboratories,, Inc., 520 F.3d 1358, 1364 (Fed. Cir. 2008). This argument is moot in light of Petitioner's alternative reliance upon Miller's diode to measure the temperature of Atkinson's DRAM. Pet. 20.

Patent Owner also argues that Miller is not part of any combination and that no motivation is given by Petitioner to combine Atkinson with Miller. Prelim. Resp. 22. As discussed above, however, we interpret the ground of unpatentability as including Miller. Petitioner has sufficiently shown, at this stage of the proceeding, that it would have been obvious to use the diode described in Miller to read and measure the temperature of Atkinson's DRAM. Pet. 20–21. On the record before us, we persuaded that Petitioner has provided articulated reasoning with rational some underpinning sufficient to support the legal conclusion of obviousness based on Atkinson, Broadwater, and Miller. See KSR, 550 U.S. at 418.

For the foregoing reasons, we determine the information presented shows a reasonable likelihood that Petitioner would prevail in establishing that the subject matter of claims 2, 4, 10, 11, 14, 15, and 17 would have been obvious over the combination of Atkinson, Broadwater, and Miller.

## D. Remaining Grounds

Petitioner argues that the challenged claims are unpatentable under 35 U.S.C. § 103 as obvious over (1) Atkinson alone; (2) Tillinghast and Broadwater; and (3) Kodama and Lee '970 or Broadwater. Pet. 12–28, 33–61. The Board's rules for AIA *inter partes* proceedings, including those pertaining to institution, are "construed to secure the just, speedy, and inexpensive resolution of every proceeding." 37 C.F.R. § 42.1(b); *accord* 35 U.S.C. §§ 316(b) (regulations for AIA *inter partes* proceedings take into account "the efficient administration of the Office" and "the ability of the Office to timely complete [instituted] proceedings"). Because we institute an *inter partes*

<sup>&</sup>lt;sup>9</sup> See supra notes 3 & 4.

review of these claims based on the grounds discussed above, we exercise our discretion not to institute a review based on these grounds for reasons of administrative expediency to ensure timely completion of the instituted proceeding. See 37 C.F.R. § 42.108(a) ("the Board may authorize the review to proceed . . . on all or some of the grounds of unpatentability asserted for each claim"); 35 U.S.C. § 314(a) (authorizing institution of an *inter partes* review under particular circumstances, but not requiring institution under any circumstances); Harmonic Inc. v. Avid Tech., Inc., 815 F.3d 1356, 1368 (Fed. Cir. 2016) ("[U]nder [37 C.F.R. § 42.108(a)], it is clear that the Board may choose to institute some grounds and not institute others as part of its comprehensive institution decision.").

#### III. CONCLUSION

For the foregoing reasons, we determine that the information presented establishes a reasonable likelihood that Petitioner would prevail in showing that claims 1–17 of the '057 patent are unpatentable. At this preliminary stage, we have not made a final determination with respect to the patentability of the challenged claims or any underlying factual or legal issues.

#### IV. ORDER

ORDERED that pursuant to 35 U.S.C. § 314(a), an *inter partes* review is hereby instituted as to claims 1–17 of the '057 patent on the following grounds of unpatentability:

| Reference(s) | Basis    | Challenged Claims  |

|--------------|----------|--------------------|

| Atkinson and | § 103(a) | 1, 3, 5-9, 12, 13, |

| Broadwater   |          | and 16             |

| Atkinson,       | § 103(a) | 2, 4, 10, 11, 14, 15, |

|-----------------|----------|-----------------------|

| Broadwater, and |          | and 17                |

| Miller          |          |                       |

FURTHER ORDERED that pursuant to 35 U.S.C. § 314(c) and 37 C.F.R. § 42.4, notice is hereby given of the institution of a trial commencing on the entry date of this decision; and